聯發科3納米芯片2024年量產,集成電路設計賽道迎來新一輪競速

聯發科正式確認其下一代旗艦移動平臺將采用臺積電3納米制程工藝,并計劃于2024年下半年投入量產。這一消息的公布,不僅標志著移動芯片制程工藝即將邁入全新階段,更將全球半導體行業的目光聚焦于高端集成電路設計領域的激烈角逐,壓力無疑已傳導至其主要競爭對手——高通。

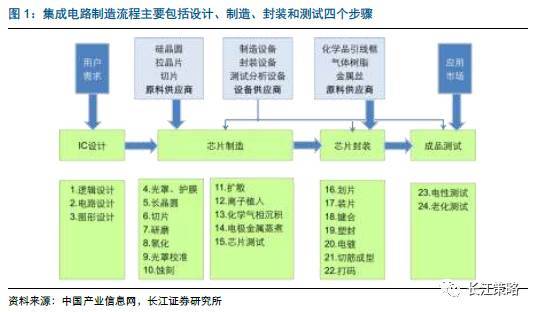

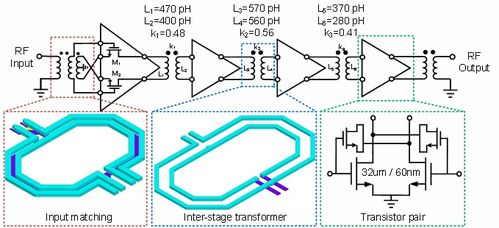

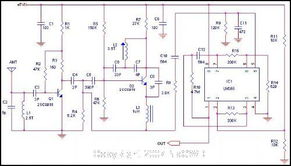

隨著智能手機市場從增量競爭轉向存量博弈,性能、能效與AI算力已成為決定旗艦產品體驗的核心。聯發科此番率先官宣3納米量產時間表,意在搶占技術制高點,重塑其在高端市場的品牌形象與技術話語權。臺積電的3納米工藝相比現行的4納米,預計將在晶體管密度提升約70%,在相同功耗下性能提升10%-15%,或在相同性能下功耗降低25%-30%。這為聯發科設計更強大、更省電的SoC(系統級芯片)提供了堅實的物理基礎,有望在能效比這一關鍵指標上實現顯著突破。

壓力由此給到了高通。作為移動芯片領域的長期領導者,高通近年來在旗艦平臺上也面臨著激烈的競爭與挑戰。盡管其驍龍系列憑借強大的GPU性能和完整的生態合作體系保持著優勢,但在制程工藝的率先采用上,聯發科的激進路線構成了直接威脅。高通下一代旗艦芯片(預計為驍龍8 Gen 4)的制程選擇與量產時間,將成為市場關注的焦點。業內普遍預計,高通很可能同樣轉向臺積電的3納米工藝(或部分采用),一場關于性能調校、能效優化與AI架構創新的“貼身肉搏”將在2024年全面展開。

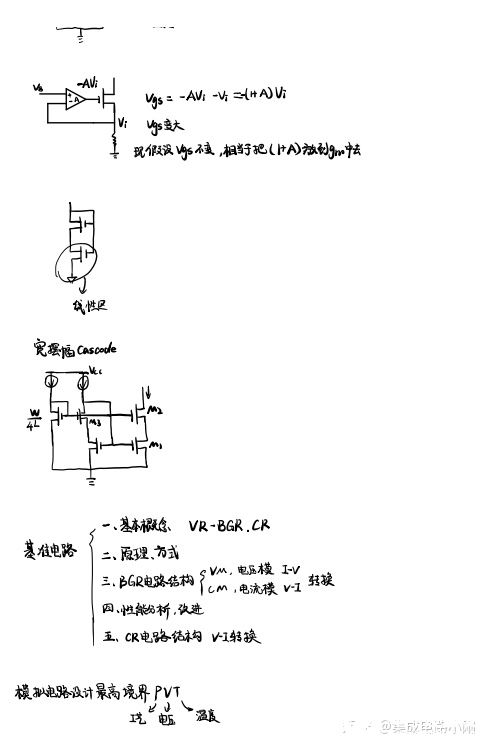

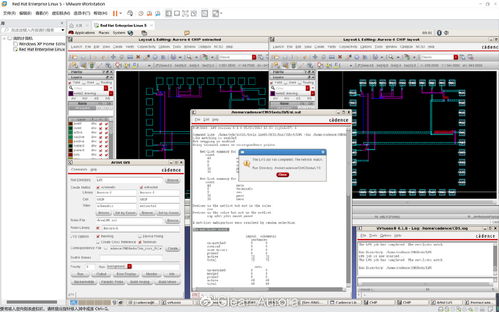

這場競賽的深遠影響,遠不止于兩家設計巨頭的市場份額之爭。它深刻揭示了全球集成電路設計行業的發展趨勢:先進制程的軍備競賽已進入白熱化階段,設計公司必須與晶圓代工廠達成深度、排他性的戰略合作,以獲取稀缺的先進產能和工藝優化支持,技術壁壘與供應鏈門檻被進一步抬高。單純追求制程數字的進步已不足以構成絕對優勢,設計能力的重要性愈發凸顯。如何在3納米的物理基礎上,通過創新的CPU/GPU/NPU架構、先進封裝技術(如Chiplet)以及軟硬件協同優化,挖掘出極致的性能與能效,才是真正的勝負手。隨著手機市場增長趨緩,芯片的應用場景正加速向汽車、XR(擴展現實)、物聯網、個人計算設備等多元化領域拓展。3納米等高階工藝所帶來的算力與能效紅利,將成為驅動這些下一代智能終端發展的核心引擎。

聯發科的率先宣言,如同一塊投入靜湖的巨石,激起了層層漣漪。它預示著2024年將成為移動芯片乃至整個高端集成電路設計領域的一個關鍵年份。無論是聯發科意圖憑借工藝領先實現高端市場的進一步突破,還是高通如何捍衛其王座并予以回應,亦或是蘋果A系列芯片的持續演進,都將共同推動著半導體技術的邊界向前拓展。這場由最前沿制程工藝驅動的設計競賽,其成果將轉化為億萬消費者手中設備更強大的計算能力、更持久的續航體驗和更智能的交互方式,持續塑造著我們的數字生活。

如若轉載,請注明出處:http://www.blnk.com.cn/product/79.html

更新時間:2026-04-06 10:21:11